Cypress is the worldwide market leader in synchronous SRAM. Cypress offers a wide portfolio including standard synchronous SRAM, No Bus Latency SRAM, and QDR® SRAM with a variety of speeds, word widths, densities, and packages. As a top-tier manufacturer, Cypress complements its products with best-in-class manufacturing and customer support.

Cypress is the worldwide market leader in synchronous SRAM. Cypress offers a wide portfolio including standard synchronous SRAM, No Bus Latency SRAM, and QDR® SRAM with a variety of speeds, word widths, densities, and packages. As a top-tier manufacturer, Cypress complements its products with best-in-class manufacturing and customer support.

|

High-performance systems, such as enterprise routers and switches, demand high random access memory performance. Cypress's QDR® SRAM is optimized for high random access performance to enable next generation networks and other high-performance systems. |

|

The QDR Consortium defines Quad Data Rate SRAM specifications. Participating companies develop pin- and function- compatible products ensuring multiple sources for customers. As a founding member, Cypress leads the definition of new standards in the QDR Consortium. |

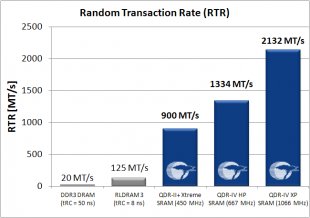

Random Transaction Rate (RTR) is the number of fully random read or write transactions a memory can perform every second. It is measured in MT/s, or mega transactions per second. RTR is a critical metric in high performance applications, such as networking, where memory access is unpredictable.

|

The QDR SRAM architecture provides the random memory access capabilities needed for networking and other high performance applications. In these applications, memory is a major bottleneck to reaching higher system performance. For example, in networking applications, each data packet requires several random memory transactions. Therefore, the packet processing rate of the system is dependent on how quickly the system can access memory. Cypress's QDR SRAM provides the RTR necessary to break system bottlenecks.

QDR SRAM, on the other hand, is designed specifically for maximum RTR. QDR SRAM allows access to any two memory locations on every clock cycle, and performance never depends on which memory location was accessed in the previous clock cycle. With QDR SRAM, RTR is guaranteed. Cypress's QDR-IV SRAM provides RTR up to 2132 MT/s. This level of performance is critical to enable the next generation of high performance systems. |

Cypress QDR SRAM provides fully random memory access |

Cypress Synchronous SRAM provides the true random memory access capabilities needed for networking and other high performance applications. In addition, Cypress Synchronous SRAM is available with a number of features that are engineered to solve networking and high performance computing challenges.

QDR SRAM is equipped with dual independent data ports to maximize memory access rates. The two ports operate concurrently, enabling both a read and write operation to occur during the same clock cycle. Access to each port is provided through a common address bus. Addresses for each port are latched on alternate rising edges of the input clock. One port is dedicated to read operations and the other is dedicated to write operations.

The data ports on QDR SRAM have double data rate (DDR) interfaces that perform two transfers per clock cycle. With two DDR data ports, QDR SRAM performs four transfers per clock cycle.

The data ports on QDR SRAM have double data rate (DDR) interfaces that perform two transfers per clock cycle. With two DDR data ports, QDR SRAM performs four transfers per clock cycle.

On-Die Termination improves signal integrity, saves board space, and reduces cost compared to external termination resistors. In high speed systems without proper signal termination, electrical signals are reflected when they reach the end of a transmission path, producing noise that lowers signal quality and reduces performance. These reflections can be reduced by attaching a resistor to the end of the transmission line. However, adding external resistors consumes board space, complicates board routing, and increases cost. ODT addresses these challenges by embedding the termination resistors within the SRAM die, which provides proper signal termination and enables high speed signaling without adding external components.

QDR-IV SRAM implements on-chip ECC error detection and correction circuitry to provide data integrity. All single-bit memory errors, including those caused by cosmic rays and alpha particles, are detected and corrected by the on-chip circuitry. The resulting soft error rate (SER) is expected to be less than 0.01 FITs/Mb. QDR-IV offers a programmable address parity feature to provide integrity on the address bus.

QDR-IV SRAM provides address and data bus inversion to reduce simultaneous switching noise and I/O power consumption. With this feature, the number of 0's and 1's in every data word or address are counted just prior to transfer. If more than half the pins in the group are 0's, then the bus is inverted and the inversion pin is set. Bus inversion ensures that no more than half of the pins switch between transfers. Less pin switching reduces noise and power consumption. This feature is programmable and can be enabled or disabled for the address and data bus independently.

QDR-IV SRAM provides a training sequence for per-bit de-skew. De-Skew training is an iterative algorithm for assessing and eliminating the skew (differences in arrival times) between multiple data signals.

QDR-IV XP SRAM contains a memory array divided into eight banks. Banking enables faster RTR and higher operating frequencies. Each of the two ports can access one bank per clock cycle, as long as both ports don't access the same bank in the same cycle. QDR-IV is also available without banking operation (HP version).

Other memory technologies are optimized for high density. Although these memories perform well for compute applications as the main memory, they do not meet the needs of high performance applications that demand high RTR.

Other memory technologies are optimized for high density. Although these memories perform well for compute applications as the main memory, they do not meet the needs of high performance applications that demand high RTR. In computing, DDR3 SDRAM, an abbreviation for double data rate type three synchronous dynamic random access memory, is a modern kind of dynamic random access memory (DRAM) with a high bandwidth interface. It is one of several variants of DRAM and associated...

In computing, DDR3 SDRAM, an abbreviation for double data rate type three synchronous dynamic random access memory, is a modern kind of dynamic random access memory (DRAM) with a high bandwidth interface. It is one of several variants of DRAM and associated...